Advanced SoC Interconnect IP Enables Greater Flexibility in an Era of Consolidation

, 2013年02月28日

The one lesson learned is that flexibility for SoC designs is increasingly more important. In this new era, companies must be able to respond to dynamic and ever-changing market demands. The consolidation experienced in 2012 taught us this lesson well. Sales channels are more fluid than ever, and companies must proactively embrace changing industry demands. Furthermore, a professionally designed interconnect fabric will give chip designers the tools they need be more competitive.

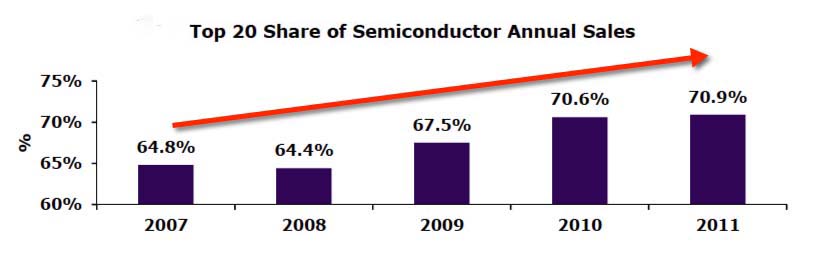

Consolidation in the market has contributed to the concentration shown in figure 1. Source GSA 2012

The consolidation we witnessed in 2012 means fewer players to battle it out, especially in the mobile-applications processor segment. At least two of the industry’s most vaunted products are gone. Fewer players are wielding greater influence in the high-end smartphone and tablet markets, and smaller players will need greater agility in their design strategies to capture emerging growth opportunities as well as introduce features that make them unique.

Flexibility is the one of the greatest assets in competing for design wins. The largest players in the industry are gaining an advantage through the interconnect portions of their chips. Due to a growing complexity and greater number of IP blocks that need to be connected, designers are required to create extremely complicated products. Some of the most successful design teams in the industry have learned that their internally designed interconnect are inadequate to link all of the elements and get the peak performance that customers demand.

In 2013, many of the companies that once designed multiple SoCs to address the needs of a variety of different customers will migrate to a single platform strategy because of the rising costs of silicon. This single-platform approach requires greater options so that chips can be reconfigured on the fly to address multiple markets.

We’ve come to realize that companies need to redesign portions of their SoCs twice as often as they previously did. Consider the challenge this brings to the design team, as many are experiencing shrinking resources. Teams must have the ability to incorporate engineering change orders (ECOs) in as little as two weeks prior to RTL freeze. Last year we witnessed this with several of our customers. Late-breaking ECOs came first from the internal marketing team and then again from the system vendor. This required chip designers to use the interconnect fabric to incorporate elements into the SoC so that the chip was better suited to meet specific markets demand. The ability to make these last-minute changes resulted in a design that captured market share because they could now hit specific functions with the right mix of features, performance, cost and power consumption.

What designers need in this environment is an interconnect that decouples the IP from the interconnect. Designers will learn that once this is possible, they can start making incremental changes at an accelerated pace. This is a powerful capability for SoC designers who want to hit multiple design targets with a single SoC platform.

The limitations of in-house interconnect designs and bundled IP are becoming increasingly evident. A lack of flexibility in the late stages of a design or the inability to use a single SoC platform to address multiple markets has left some companies sitting on the sidelines while more nimble players reap the rewards.

While 2013 signals return to growth, it’s also important to remember that companies must think more strategically about SoC design. Agility and flexibility are required to differentiate companies from the competition because time to market combined with the right features are often the difference between success and failure.